Diseño integrado con FPGA:Implementación

La disponibilidad de FPGA más potentes y entornos de programación más efectivos ha hecho que la implementación de FPGA ampliamente accesible, pero el uso de FPGA puede parecer abrumador.

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

1:Recursos de hardware

2:Idiomas de implementación

3:Proceso de desarrollo

4:Construyendo un proyecto

5:Implementación (este artículo)

Adaptado de Architecting High-Performance Embedded Systems, por Jim Ledin.

Prueba del comportamiento lógico

Es importante probar el comportamiento de la lógica mediante simulación antes de intentar ejecutarla en la FPGA. Esto se debe a que es mucho más fácil detectar y solucionar problemas en el entorno de simulación que con la lógica que se ejecuta dentro de la FPGA. Las herramientas de simulación de Vivado hacen un muy buen trabajo al representar el comportamiento del circuito:

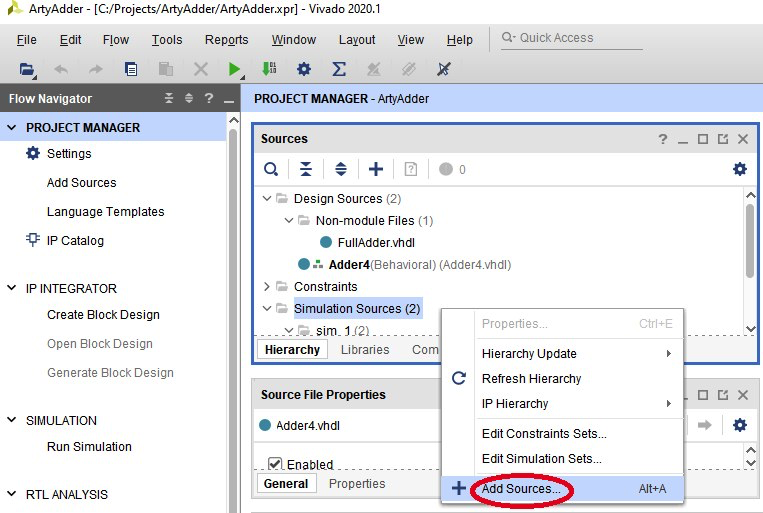

- En Fuentes subventana, haga clic con el botón derecho en Fuentes de simulación y seleccione Agregar fuentes… :

Figura 4.18 - Agregar fuentes… selección de menú para Fuentes de simulación

- En Agregar fuentes cuadro de diálogo, asegúrese de Agregar o crear fuentes de simulación está seleccionado, luego haga clic en Siguiente .

- En Agregar o crear fuentes de simulación cuadro de diálogo, haga clic en Crear archivo .

- Ingrese el nombre de archivo vhdl y haz clic en Aceptar .

- Haga clic en Finalizar . para descartar Agregar o crear fuentes de simulación cuadro de diálogo y, a continuación, haga clic en Aceptar en Definir módulo cuadro de diálogo y haga clic en Sí cuando se le pregunte si está seguro de que desea utilizar estos

- Haga doble clic en Adder4 TestBench (Behavioural) (Adder4TestBench.vhdl) . en Fuentes de simulación . Elimina los contenidos rellenados automáticamente del vhdl . ventana del editor e introduzca el siguiente código en Adder4TestBench.vhdl editor:

biblioteca IEEE; utilice IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entidad ADDER4_TESTBENCH es la entidad final ADDER4_TESTBENCH; la arquitectura BEHAVIORAL de ADDER4_TESTBENCH es el componente ADDER4 es el puerto (A4:en std_logic_vector (3 downto 0); Blogic:en std_logic_ownto 0); 0); C_OUT4:fuera std_logic); componente final; señal a:std_logic_vector (3 hacia abajo 0); señal b:std_logic_vector (3 hacia abajo 0); señal s:std_logic_vector (3 hacia abajo 0); señal c_out:std_logic; señal suma_esperada5:sin firmar (4 hacia abajo a 0); señal suma_esperada4:sin firmar (3 hacia abajo a 0); señal esperaba_c:std_logic; error de señal:std_logic; begin TESTED_DEVICE:ADDER4 port map (A4 => a, B4 => b, SUM4 => s, C_OUT4 => c_out); PRUEBA:inicio del proceso - Pruebe todas las combinaciones de dos sumandos de 4 bits (256 pruebas en total) para a_val en 0 a 15 bucles para b_val en 0 a 15 bucles - Configure las entradas para el componente ADDER4 a <=std_logic_vector (to_unsigned ( a_val, a'length)); b <=std_logic_vector (to_unsigned (b_val, b'length)); espere 1 ns; - Calcule la suma de 5 bits de los dos valores de 4 bits suma_esperada5 <=sin signo ('0' &a) + sin signo ('0' &b); espere 1 ns; - Divida la suma en una salida de 4 bits y un bit de acarreo suma_esperada4 <=suma_esperada5 (3 hacia abajo a 0); c_esperado <=suma_esperada5 (4); espere 1 ns; - La señal de 'error' solo irá a 1 si ocurre un error si ((unsigned (s) =unsigned (esperaba_sum4)) y (c_out =esperaba_c)) entonces error <='0'; más error <='1'; terminara si; - Cada pasada a través del bucle interior tarda 10 ns, espere 7 ns; bucle final; bucle final; Espere; TEST de proceso final; COMPORTAMIENTO de arquitectura final; Este código ejercita la funcionalidad de sumador de 4 bits presentando todas las combinaciones de números de 4 bits a cada uno de los A4 y B4 entradas al Adder4 componente. Compara el SUM4 y C_OUT4 resultados del Adder4 componente a valores calculados de forma independiente para las mismas entradas. Después de cada operación de adición, el error la señal se establece en 0 si el Adder4 los resultados coincidieron con los valores esperados o se estableció en 1 si hay una discrepancia.

El código en Adder4TestBench.vhdl se asemeja al código de software tradicional en la forma en que utiliza bucles for anidados para aplicar todas las combinaciones de entrada de prueba al Adder4 componente bajo prueba. El código que ejecuta pruebas en modo de simulación no es sintetizable, lo que significa que no representa puramente un circuito lógico de hardware y es capaz de realizar operaciones tradicionales similares al software, como la ejecución iterativa de para bucles.

Sin embargo, como en los circuitos físicos, las señales a las que se les asignan valores en el código del banco de pruebas usando el operador <=no pueden usarse en el mismo instante en el tiempo en expresiones posteriores. Esto se debe a que el entorno de simulación representa los efectos del retardo de propagación en el mundo real, que es significativo incluso dentro de pequeños dispositivos FPGA. Los tres esperan 1 ns ; Las declaraciones en el banco de pruebas codifican las operaciones del circuito de pausa para permitir el retardo de propagación. Estos retrasos de 1 ns proporcionan tiempo para los valores de señal calculados justo antes de la espera. declaración para propagar para que se puedan utilizar en la siguiente declaración. El final espera 7 ns. ; La declaración en el bucle interno es una pausa que nos permite ver claramente los resultados de cada iteración de los bucles de simulación en la pantalla de seguimiento de señal.

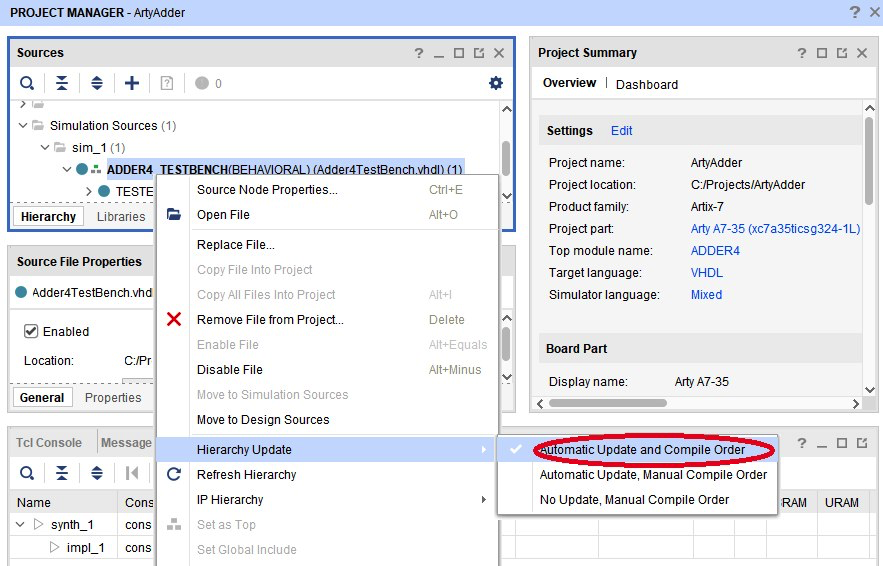

- Haga clic con el botón derecho en Adder4 TestBench (Behavioural) (Adder4TestBench.vhdl) en Fuentes de simulación y seleccione Actualización automática y orden de compilación . Esto establece ADDER4_TESTBENCH como objeto de nivel superior para la ejecución de la simulación:

Figura 4.19 - Selección de menú para configurar Actualización automática y Orden de compilación

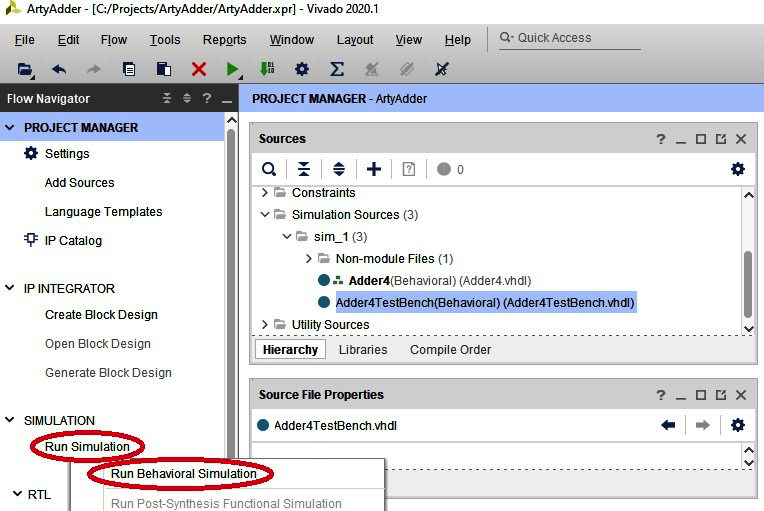

- Haga clic en Ejecutar simulación . y luego Ejecutar simulación de comportamiento en el Flow Navigator ventana para ingresar al modo de simulación. Si aún no ha guardado los archivos del editor, se le pedirá que lo haga. Haga clic en Guardar . . A continuación, se ejecutará la simulación:

Figura 4.20 - Selección del menú Ejecutar simulación de comportamiento

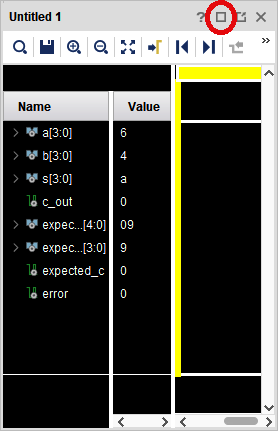

- Cuando la SIMULACIÓN se abre la ventana, haga clic en el botón maximizar en la ventana de salida de la simulación con el título Sin título 1 :

Figura 4.21 - Ventana de resultados de la simulación

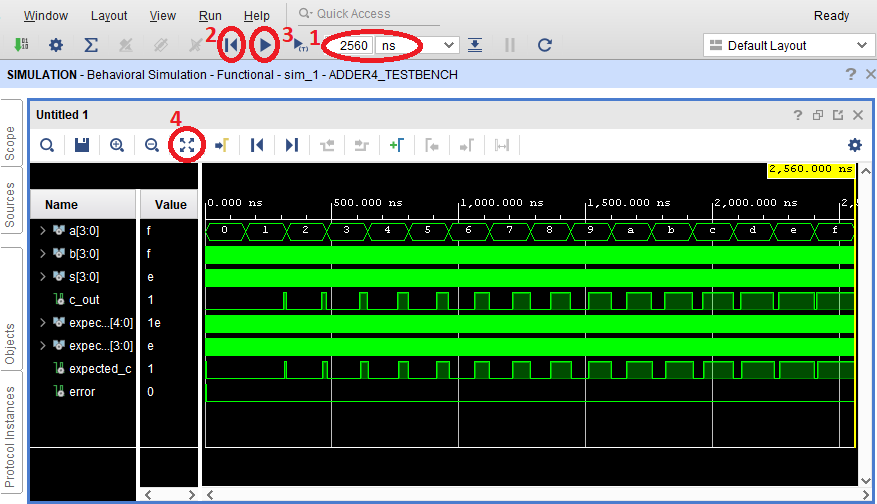

El tiempo total simulado de cada pasada a través del bucle interior es de 10 ns. Porque hay 256 pases a través del bucle en Adder4TestBench.vhdl , el tiempo para ejecutar la simulación es de 2560 ns.

- Establezca el tiempo de ejecución de la simulación en 2560 ns en la barra de herramientas superior ( paso 1 en la siguiente figura), presione el botón de reinicio que apunta a la izquierda ( paso 2 ) y, a continuación, presione el botón que mira hacia la derecha para ejecutar la simulación durante 2560 ns ( paso 3 ) y, finalmente, presione el botón Zoom Fit botón ( paso 4 ) para escalar el rango de datos de salida de la simulación para que se ajuste a la ventana:

Figura 4.22 - Resultados de la simulación desde el principio hasta el final de la ejecución

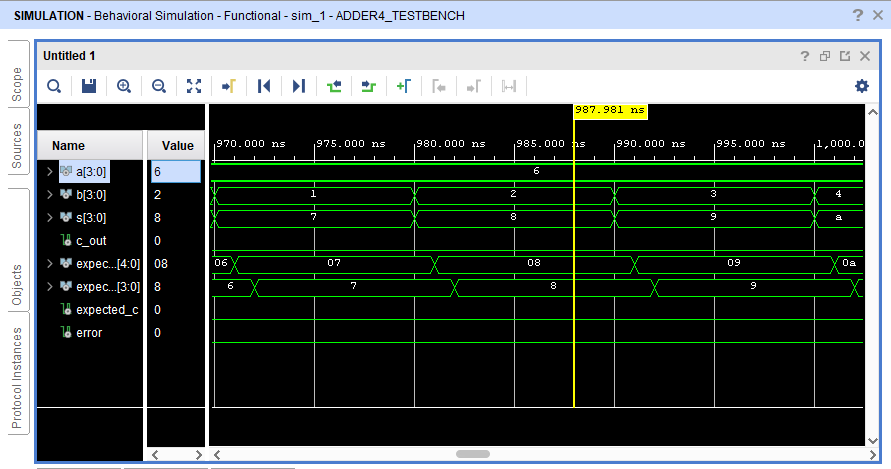

Puede utilizar los iconos de lupa para acercar cualquier punto de la traza y observar los resultados de cada operación de adición realizada durante la prueba. Por ejemplo, la siguiente figura muestra los valores decimales 6 y 2 que se agregaron para producir el resultado 8 con un acarreo de 0. Estos valores coinciden con los valores esperados, lo que provocó el error que se establezca en 0. El error la señal es 0 para los 256 casos de prueba, lo que indica que nuestro circuito lógico pasó todas las pruebas:

Figura 4.23 - Vista ampliada de los resultados de la simulación

- Cierre el modo de simulación haciendo clic en la X en el SIMULACIÓN azul barra sobre el seguimiento de datos Haga clic en Aceptar cuando se le pregunte si desea cerrar la simulación.

Una vez superadas las pruebas de comportamiento, definiremos las señales de E / S utilizadas en el diseño.

Definición de señales de E / S

Nuestro siguiente paso es conectar las entradas y salidas de nuestro circuito a los dispositivos de hardware en la placa Arty. Las entradas serán los interruptores de la placa y los botones, y las salidas serán los LED.

Los siguientes pasos crearán un archivo de restricciones que describe los pines de E / S que usaremos en el dispositivo FPGA y las funciones conectadas a esos pines en la placa Arty. Los archivos de restricción tienen la extensión xdc:

- En Fuentes subventana, haga clic con el botón derecho en Restricciones y seleccione Agregar fuentes… .

- En Agregar fuentes cuadro de diálogo, asegúrese de Agregar o crear restricciones está seleccionado, luego haga clic en Siguiente .

- En Agregar o crear restricciones cuadro de diálogo, haga clic en Crear archivo .

- Ingrese el nombre de archivo Arty-A7-100.xdc (o Arty-A7-35.xdc si es apropiado para su dispositivo) y haga clic en Aceptar .

- Haga clic en Finalizar . para descartar Agregar o crear restricciones

- Expanda las restricciones árbol de origen y haga doble clic en Arty-A7-35.xdc .

- Digilent proporciona archivos de restricción rellenados previamente para los tableros Arty A7. Visite https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc y copie todo el contenido de la ventana del navegador en la ventana del editor Arty-A7-35.xdc en Vivado. Si es apropiado para su dispositivo, use el archivo en https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc en su lugar.

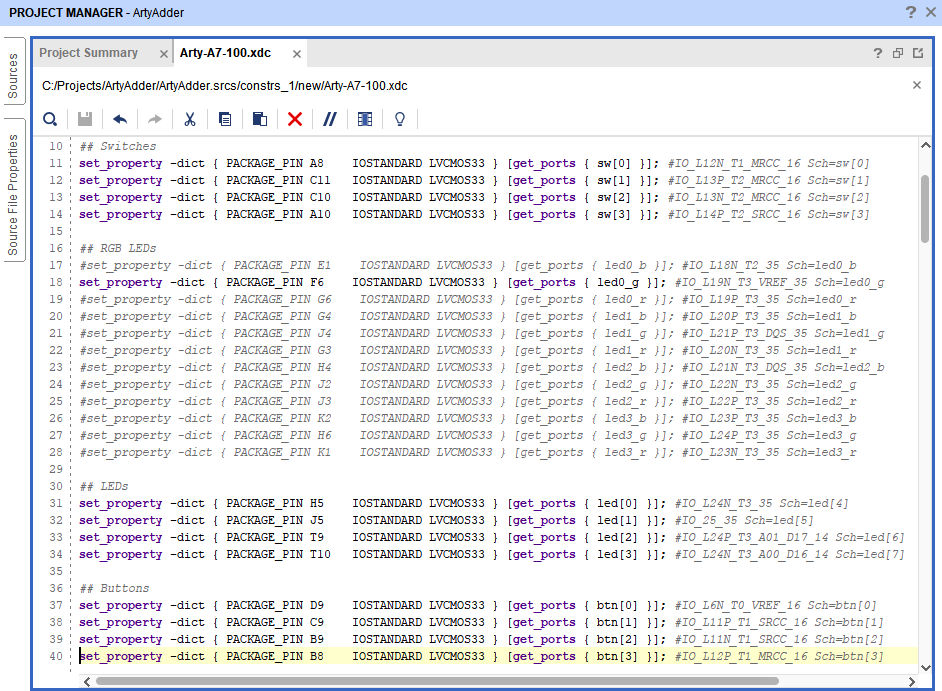

- Todos los pines de E / S se comentan en el archivo de restricciones. Descomente las líneas correspondientes del archivo eliminando el carácter # del principio de cada línea. Usaremos los pines enumerados en las siguientes secciones en el Arty- A7-100.xdc file: Cambios , RGB LED (pero solo led0_g , el primer LED verde), LED y botones . La siguiente figura muestra estas líneas después de haberlas descomentado:

Figura 4.24 - Ventana del editor de restricciones

En la siguiente sección, crearemos un archivo VHDL de nivel superior que interconecta el código del sumador con los dispositivos de E / S.

Creación de un archivo VHDL de nivel superior

A continuación, crearemos un archivo VHDL de nivel superior que conecta nuestro componente sumador de 4 bits a las señales de E / S de la placa correspondiente:

- En Fuentes subventana, haga clic con el botón derecho en Fuentes de diseño y seleccione Agregar fuentes… .

- En Agregar fuentes cuadro de diálogo, asegúrese de Agregar o crear fuentes de diseño está seleccionado, luego haga clic en Siguiente .

- En Agregar o crear fuentes de diseño cuadro de diálogo, haga clic en Crear archivo .

- Ingrese el nombre de archivo vhdl y haz clic en Aceptar .

- Haga clic en Finalizar . para descartar Agregar o crear fuentes de diseño cuadro de diálogo y, a continuación, haga clic en Aceptar en Definir módulo cuadro de diálogo y haga clic en Sí cuando se le pregunte si está seguro de que desea utilizar estos

- Haga doble clic en vhdl . en Fuentes de diseño . Elimina los contenidos rellenados automáticamente de ArtyAdder.vhdl ventana del editor e introduzca el siguiente código en ArtyAdder.vhdl editor:

- Cargue la biblioteca de bibliotecas estándar IEEE; use IEEE.STD_LOGIC_1164.ALL; la entidad ARTY_ADDER es el puerto (sw:en STD_LOGIC_VECTOR (3 hacia abajo a 0); btn:en STD_LOGIC_VECTOR (3 hacia abajo a 0); led:hacia fuera STD_LOGIC_VECTOR (3 hacia abajo a 0); led0_LOGIC:hacia fuera) entidad STD ARTY_ADDER; la arquitectura BEHAVIORAL de ARTY_ADDER es - Consulte la definición anterior del componente sumador de 4 bits ADDER4 es puerto (A4:en std_logic_vector (3 downto 0); B4:en std_logic_vector (3 downto 0); SUM4:out std_logic_vector (3 downto 0); C_OUT4:out std_logic); componente final; begin ADDER:ADDER4 port map (A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g); arquitectura final BEHAVIORAL;

Este código asigna los nombres de las señales para los dispositivos de E / S nombrados en Arty-A7-100.xdc como sw (4 interruptores), btn (4 botones), led (4 LED de un solo color) y led0_g (el canal verde del primer LED multicolor) al ADDER4 entradas y salidas.

Si bien VHDL no distingue entre mayúsculas y minúsculas, el procesamiento de xdc Los archivos de restricción en Vivado distinguen entre mayúsculas y minúsculas. El caso utilizado en los nombres de dispositivos de E / S definidos en xdc El archivo debe ser idéntico cuando se hace referencia a él en un archivo VHDL. Específicamente, los nombres de las señales de E / S en VHDL deben estar en minúsculas en este archivo porque están en minúsculas en el archivo de restricciones.

Ahora estamos listos para sintetizar, implementar y programar nuestro diseño para el tablero Arty.

Sintetizar e implementar el flujo de bits FPGA

Alternativamente, puede seleccionar Generar Bitstream y Vivado realizará todos los pasos necesarios, incluida la síntesis, la implementación y la generación de flujo de bits sin más intervención del usuario. Si ocurre un error fatal, el proceso se detendrá y se mostrarán mensajes de error. Realice los siguientes pasos para generar el flujo de bits:

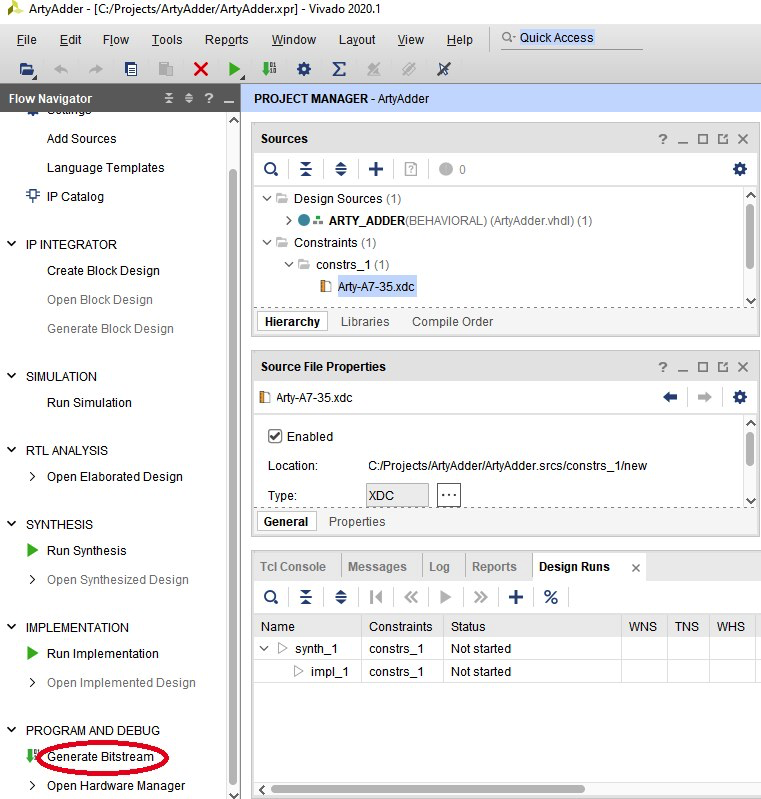

- Haga clic en Generar flujo de bits . para iniciar la compilación Es posible que se le pregunte si desea guardar los editores de texto. Haga clic en Guardar . . Es posible que se le informe que no hay resultados de implementación disponibles y se le preguntará si está bien iniciar la síntesis y la implementación. Haga clic en Sí . :

Figura 4.25 - Generar selección de menú Bitstream

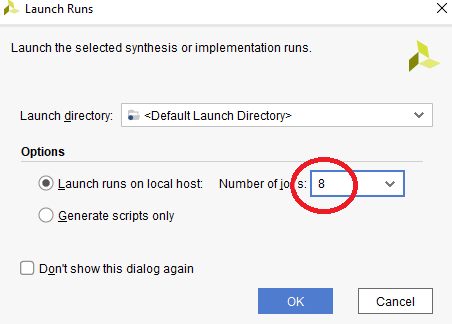

- El lanzamiento se ejecuta A continuación, aparecerá el cuadro de diálogo Puede seleccionar un valor para Número de trabajos hasta la cantidad de núcleos de procesador en su computadora. El uso de más núcleos hace que el proceso sea más rápido, pero puede atascar su máquina si desea continuar usándola durante un proceso de compilación prolongado. Haga clic en Aceptar . para comenzar la compilación:

Figura 4.26 - Cuadro de diálogo Ejecuciones de inicio

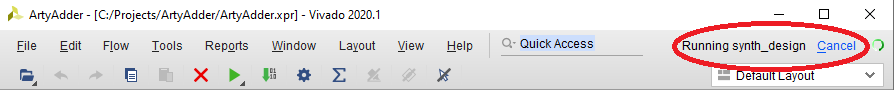

- Durante el proceso de construcción, Vivado mostrará el estado en la esquina superior derecha de la ventana principal. Si es necesario, puede cancelar el proceso de compilación haciendo clic en Cancelar junto a la pantalla de estado:

Figura 4.27 - Visualización del estado de la compilación

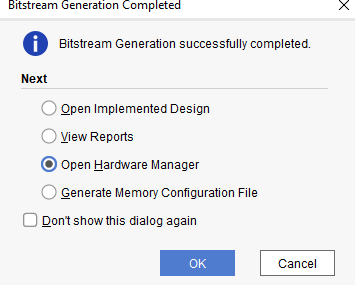

- Cuando se completa el proceso de compilación, asumiendo que no hubo errores fatales, una Generación de Bitstream Completada dialog will Aunque se ofrecen otras opciones, procederemos directamente a descargar el bitstream a la placa Arty. Seleccione Abrir Administrador de hardware . y haz clic en Aceptar :

Figura 4.28 - Cuadro de diálogo Generación de flujo de bits completada

A continuación, descargaremos el flujo de bits en la FPGA.

Descarga del flujo de bits al tablero

Realice los siguientes pasos para descargar el flujo de bits a una placa Arty A7:

- El ADMINISTRADOR DE HARDWARE Aparecerá un cuadro de diálogo que indicará No hay ningún destino de hardware abierto .

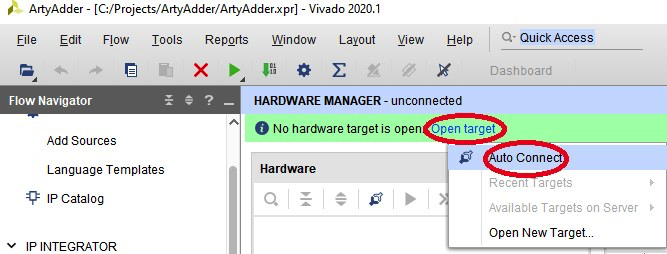

- Conecte su placa Arty A7-35 o A7-100 a la computadora con un USB. Espere unos segundos hasta que se reconozca la placa, luego haga clic en Abrir objetivo , luego Conexión automática :

Figura 4.29 - Abrir selecciones de destino y conexión automática

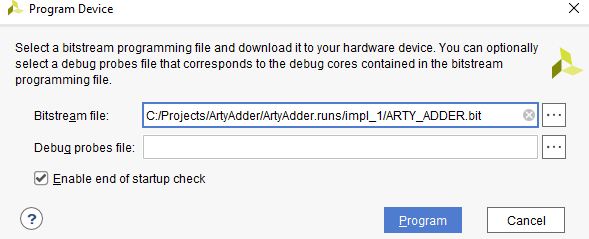

- Después de unos segundos, Vivado debería indicar que la placa está conectada. Haga clic en Programar dispositivo . para descargar el flujo de bits FPGA al Arty Se le pedirá que seleccione un archivo de flujo de bits. Si ha utilizado la misma estructura de directorio que en este ejemplo, el archivo se ubicará en C:/ Projects / ArtyAdder / ArtyAdder.runs / impl_1 / ARTY_ADDER.bit :

Figura 4.30 - Cuadro de diálogo Programar dispositivo

- Haga clic en Programa . para descargar el programa al dispositivo FPGA e iniciarlo

- Ahora puede probar el funcionamiento del programa con Arty I / O Coloque los cuatro interruptores en apagado posición (mueva los interruptores hacia el borde del tablero adyacente) y no presione ninguno de los cuatro botones. Los cuatro LED verdes deben estar apagados.

- Si enciende cualquier interruptor individual o presiona cualquier botón, el LED verde correspondiente debería encenderse. Si enciende cualquier combinación de interruptores mientras presiona cualquier número de botones, se agregarán los números de 4 bits correspondientes y se iluminarán los LED con el Si hay un acarreo (por ejemplo, encienda SW3 y presione BTN3 simultáneamente), el LED verde de transporte se iluminará.

El proceso de programación realizado aquí almacenó el programa en FPGA RAM. Si apaga y enciende la placa FPGA, deberá repetir el proceso de programación para volver a cargar el programa. Alternativamente, puede almacenar el archivo de configuración FPGA en la memoria flash incorporada como se describe en la siguiente sección.

Programación del flujo de bits en la memoria flash integrada

Para configurar la FPGA cada vez que se aplica energía a la placa Arty, el archivo de configuración de la FPGA debe almacenarse en la memoria flash de la placa. Si el puente MODE está instalado, la FPGA intentará descargar un archivo de configuración desde la memoria flash incorporada en el momento del encendido. Esta memoria está ubicada en un chip separado adyacente al Artix-7 FPGA. Siga estos pasos para programar el archivo de configuración en la memoria flash:

- Instale el MODO puente en el tablero Arty si aún no está en

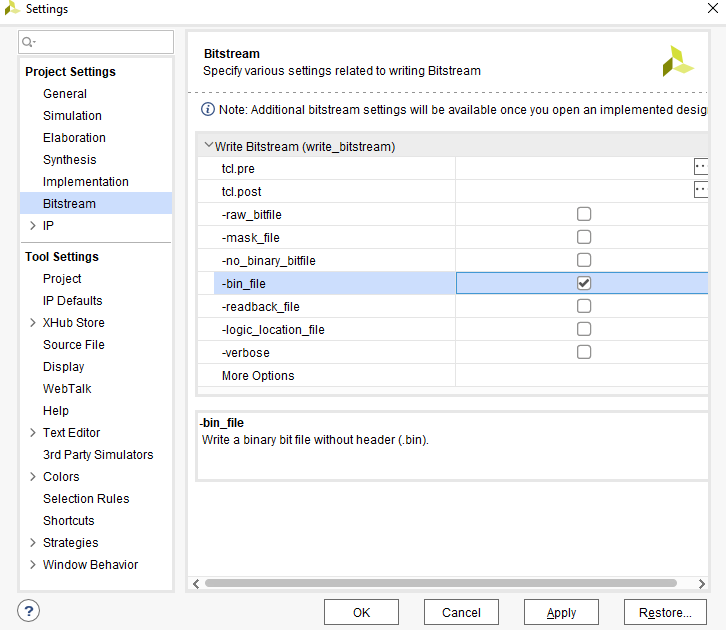

- Haga clic con el botón derecho en Generar flujo de bits . y seleccione Configuración de Bitstream ... .

- En Configuración cuadro de diálogo, marque la casilla junto a -bin_file y haz clic en Aceptar :

Figura 4.31 - Cuadro de diálogo de configuración de Bitstream

- En el cuadro de diálogo principal de Vivado, haga clic en Generar flujo de bits . y repita el proceso de generación de flujo de bits. Haga clic en Cancelar . cuando se haya completado la generación de flujo de bits diálogo

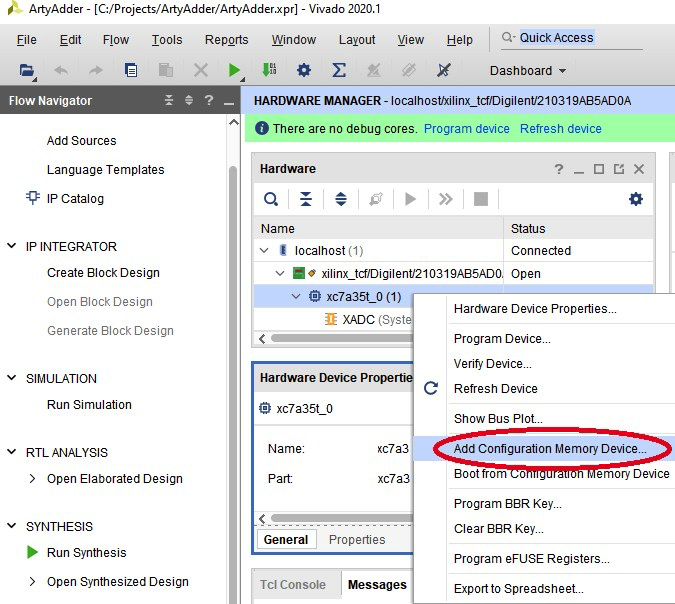

- En Hardware cuadro de diálogo, haga clic con el botón derecho en el número de pieza FPGA ( xc7a100t_0 ) y seleccione Agregar dispositivo de memoria de configuración ... :

Figura 4.32 - Agregar dispositivo de memoria de configuración… selección de menú

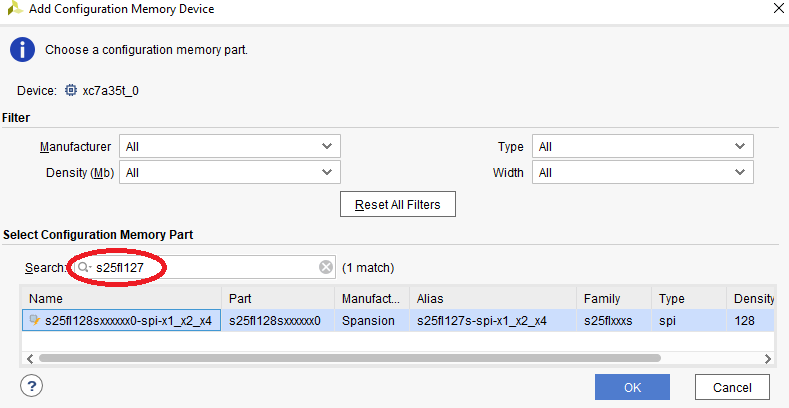

- Escribe s25fl127 en la Búsqueda Esto debería mostrar un número de pieza coincidente. Seleccione la pieza y haga clic en Aceptar . :

Figura 4.33 - Cuadro de diálogo Agregar dispositivo de memoria de configuración

- Se le presentará un cuadro de diálogo que le preguntará ¿Desea programar el dispositivo de memoria de configuración ahora? Haga clic en Aceptar . .

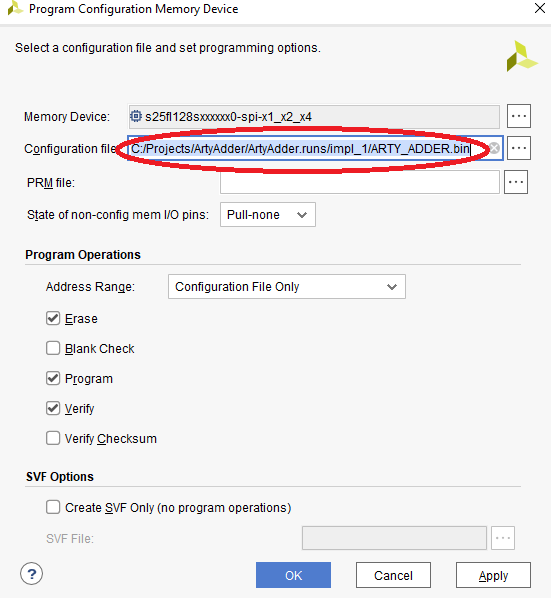

- Esto mostrará un Dispositivo de memoria de configuración del programa cuadro de diálogo que solicita el nombre del archivo de configuración. Haga clic en … botón a la derecha del Archivo de configuración y seleccione C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Haga clic en Aceptar . :

Figura 4.34 - Cuadro de diálogo Dispositivo de memoria de configuración del programa

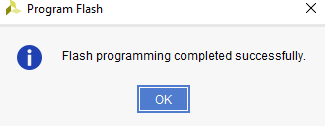

- El proceso de programación tardará varios segundos en. Debería recibir un mensaje indicando el éxito después de que el archivo se haya programado en la memoria flash de la placa:

Figura 4.35 - Diálogo de programa Flash completo

Después de esto, cada vez que apague y encienda la placa, se cargará y ejecutará el programa sumador de 4 bits. El programa tardará mucho en cargar con la configuración que usamos para cargar el archivo de configuración. Para evitar esperar a que la FPGA cargue el programa, puede mejorar la velocidad de carga del archivo de configuración realizando los siguientes pasos:

- Seleccione Abrir diseño sintetizado . en Flow Navigator .

- En el menú principal de Vivado, seleccione Herramientas / Editar propiedades del dispositivo… .

- En General , configure Habilitar compresión de flujo de bits a TRUE .

- En Configuración pestaña, establezca Velocidad de configuración (MHz) a 33, luego haga clic en Aceptar .

- Genere el flujo de bits nuevamente y programe la memoria flash como se describe. Deberá quitar el dispositivo de memoria de configuración y agregarlo nuevamente para mostrar la opción de reprogramación.

- Cerrar Hardware Gerente .

- Desenchufe el cable USB de la placa Arty y conéctelo. El programa debería comenzar a ejecutarse virtualmente instantáneamente al encenderlo.

Esta sección presentó un ejemplo de lógica combinacional simple que interactúa con señales en los pines de E / S de FPGA. La intención aquí ha sido familiarizarlo con el Vivado

conjunto de herramientas y demostrar cómo se utilizan las herramientas para realizar un ciclo de desarrollo FPGA completo.

Resumen

Este capítulo comenzó con una discusión sobre el uso efectivo de FPGA en arquitecturas de sistemas embebidos en tiempo real y continuó con una descripción de los dispositivos FPGA estándar y los componentes de bajo nivel que contienen. Se introdujo la gama de lenguajes de diseño FPGA, incluidos HDL, métodos de diagrama de bloques y lenguajes de programación de software populares como C / C ++. Se presentó un esquema del proceso de desarrollo de FPGA. El capítulo concluyó con un ejemplo completo de un ciclo de desarrollo de FPGA, comenzando con una declaración de requisitos y terminando con un sistema funcional implementado en una placa de desarrollo de FPGA de bajo costo.

Después de haber completado este capítulo, debe saber cómo se pueden aplicar los FPGA de manera efectiva en arquitecturas de sistemas embebidos en tiempo real y comprender los componentes dentro de un circuito integrado FPGA. Ha aprendido sobre los lenguajes de programación utilizados en el diseño de algoritmos FPGA, los pasos en el ciclo de desarrollo FPGA y comprende la secuencia de pasos en el proceso de desarrollo FPGA.

El próximo capítulo ampliará el proceso de desarrollo de FPGA para proporcionar un enfoque completo para la arquitectura de sistemas embebidos en tiempo real que contienen FPGA. También se iniciará el desarrollo de un prototipo de sistema embebido de alto rendimiento, un osciloscopio digital, que servirá de ejemplo para los siguientes capítulos.

Reproducido con permiso de Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT).

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT). Contenidos relacionados:

- Diseño integrado con FPGA:recursos de hardware

- Diseño integrado con FPGA:lenguajes de implementación

- Diseño integrado con FPGA:proceso de desarrollo

- Las herramientas de código abierto ayudan a simplificar la programación FPGA

- Implementación de algoritmos de punto flotante en FPGA o ASIC

- Aprovechamiento de FPGA para el aprendizaje profundo

- Las herramientas de software migran el código de la GPU a FPGA para aplicaciones de inteligencia artificial

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Qué es el diseño de sistemas integrados:pasos en el proceso de diseño

- ¿Acabado de piezas impresas en 3D con… crayones?

- Entrevista experta:Tecnólogo jefe de ANSYS sobre cómo lograr el éxito en la impresión 3D en metal con simulación

- Convertir macrodatos en datos inteligentes con IA incorporada

- Soluciones de diseño y desafíos de implementación del puerto USB tipo C

- Las tendencias clave de la industria están dando forma al diseño integrado

- La plataforma de código abierto apunta a IoT con Linux incorporado

- Clientron:TPV multifuncional con impresora integrada

- El kit de diseño mide la presión arterial con un sensor óptico

- Diseño incrustado con FPGA:lenguajes de implementación

- Todo con aditivo