Cómo aprovechar las funciones de seguridad Arm TrustZone del LPC5500

Aprenda cómo funciona la extensión Arm TrustZone para la serie LPC5500 y cómo comenzar a utilizar las medidas de seguridad en aplicaciones personalizadas seguras y no seguras.

Con dispositivos cada vez más conectados y la creciente sofisticación de los piratas informáticos, muchas empresas, como NXP Semiconductors, han reconocido la necesidad de contramedidas. NXP ha desarrollado la serie LPC5500 MCU, que viene con funciones de seguridad mejoradas que se pueden utilizar para proteger proyectos integrados.

NXP ha adoptado un generador de números aleatorios compatible con FIPS, ha seleccionado el algoritmo de descifrado "Prince" (que permite que el núcleo ejecute código cifrado simétrico) y ha implementado una clave efímera en chip de 4096 bits con tecnología PUF. Cuando se combinan con el acelerador de hardware criptográfico en chip "CASPER", las MCU LPC5500 son adecuadas para aplicaciones de IoT en el borde de la red que requieren contramedidas robustas de ciberseguridad y aprovisionamiento de claves durante todo el ciclo de vida.

Además, el chip aprovecha la tecnología Arm TrustZone para dispositivos basados en Cortex-M. En este artículo, aprenda cómo funciona la extensión TrustZone de la serie LPC5500 y cómo comenzar a utilizar las medidas de seguridad en aplicaciones personalizadas.

¿Qué es la tecnología Arm TrustZone para Cortex-M?

El principio fundamental de TrustZone se explica mejor a través de un ejemplo. El fabricante de MCU a menudo proporciona código propietario personalizado, como bibliotecas de seguridad, un cargador de arranque o algoritmos DSP rápidos en la ROM del microcontrolador. Sin embargo, los autores de estas aplicaciones a menudo tienen buenas razones para proteger su propiedad intelectual:es posible que no quieran que los usuarios o la competencia descompilen los archivos binarios para aplicar ingeniería inversa a los algoritmos.

Por un lado, los programadores quieren utilizar estas bibliotecas de software predefinidas. Sin embargo, por otro lado, el fabricante no quiere que el código quede expuesto a una parte posiblemente malintencionada.

Figura 1. El código de usuario no seguro y el contenido de la ROM segura residen en la misma MCU física.

El proveedor quiere ocultar los detalles de implementación, al mismo tiempo que se asegura de que los desarrolladores puedan acceder a las funciones. El código de usuario es capaz de llamar a los métodos expuestos del software oculto, pero no tiene acceso directo a la memoria propiedad de la ROM segura. El resultado es una estructura que consta de dos subsistemas aislados. Las transiciones entre esos dos mundos se rigen por la extensión de seguridad TrustZone.

Esto significa que un microcontrolador que utilice TrustZone se diseñará como dos proyectos separados. El primer proyecto comienza en el estado seguro. Luego configura las atribuciones de seguridad para los recursos en chip y puede publicar funciones seguras en una tabla accesible desde el estado no seguro. El segundo contiene el código no seguro y tiene acceso limitado a las funciones expuestas del mundo seguro.

Diferencias con arquitecturas anteriores

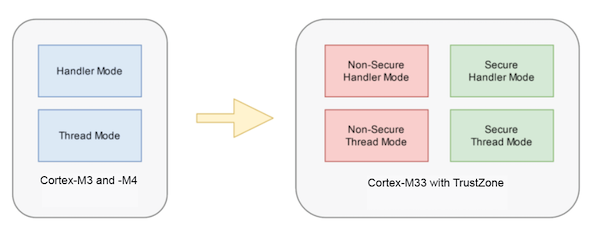

Los núcleos Cortex-M3 y -M4 conocen dos modos de procesador:modo hilo y modo controlador. El software de la aplicación se ejecuta en modo hilo y el modo controlador se ocupa de las excepciones. El código puede operar en un nivel privilegiado o no privilegiado, que controla el acceso a ciertas funciones de la CPU.

Con la extensión TrustZone en núcleos Cortex-M33, se introdujeron dos nuevos estados, como se discutió anteriormente. Ese cambio resultó en cuatro modos de procesador diferentes:controlador no seguro, modo de controlador seguro, subproceso no seguro y subproceso seguro.

Figura 2. La extensión TrustZone en el núcleo M33 crea cuatro modos de procesador.

Además de otras actualizaciones, también se introdujeron nuevos temporizadores SysTick con los nuevos estados. Entonces, ahora, hay temporizadores separados para el estado seguro y el estado no seguro.

Partición de memoria

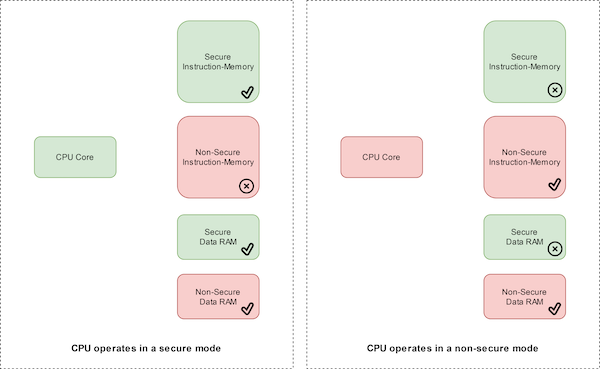

Como se mencionó anteriormente, la memoria de la MCU se divide en áreas seguras y no seguras. El núcleo de la CPU de la MCU solo puede acceder a las regiones de memoria segura si opera en uno de los modos seguros. No puede acceder a ninguna instrucción que resida en otras particiones de memoria. Sin embargo, puede leer y escribir segmentos seguros y no seguros de la RAM de datos. Si el núcleo de la CPU se encuentra en un estado no seguro, solo puede acceder a los bloques de memoria de datos e instrucciones no seguros.

TrustZone decora rangos de direcciones en el mapa de memoria con atribuciones de seguridad. Hay tres atribuciones de seguridad:seguro (S), no seguro (NS) y no seguro llamable (NSC). El acceso a cada área de memoria está permitido o denegado, según el estado de seguridad actual del núcleo.

Figura 3. La CPU puede acceder a diferentes áreas en modo seguro y no seguro.

En el dispositivo LPC55S69, la memoria se dividió en segmentos seguros y no seguros según la dirección. Si el bit 28 de la dirección de memoria es BAJO, la memoria no es segura. De lo contrario, es seguro. La única excepción es la memoria del programa, que se puede configurar a través de la Unidad de atribución de seguridad.

Los componentes básicos de una aplicación segura

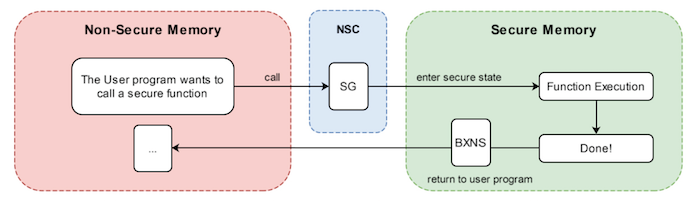

El código no seguro no puede realizar llamadas directas a la parte segura de la aplicación. En cambio, la parte segura expone una lista de funciones a las que puede acceder un usuario. Esa lista se llama tabla de chapa porque es una capa muy delgada que es visible desde el exterior, pero oculta los detalles internos. La tabla de revestimiento se encuentra en una región de memoria con el atributo TrustZone NonSecure Callable.

Por lo general, la fuente de la parte asegurada no es visible. En cambio, se compila, dando una biblioteca de objetos y la tabla de revestimiento como un archivo de encabezado. Tenga en cuenta que ninguno de estos archivos contiene ninguna de las instrucciones reales, pero juntos contienen la información necesaria para llamar a funciones seguras. La tabla de revestimiento solo contiene una puerta de enlace y una instrucción de ramificación a la ubicación de memoria segura donde residen las instrucciones reales.

Transición entre funciones seguras y no seguras

Las CPU con la extensión TrustZone admiten dos nuevas funciones para la transición entre seguro y no seguro:la instrucción SG y BXNS.

Cuando el código de usuario desea una función segura, realiza una llamada a través de la tabla de chapa, que se encuentra en la parte NSC de la memoria. Luego, la instrucción SG se utiliza para cambiar la CPU a un modo seguro. Cuando se completa la ejecución, el control vuelve al código de usuario con la instrucción BXNS:

Figura 4. El código de usuario debe llamar a una función segura a través del controlador TrustZone.

Si el usuario intenta una operación ilegal relacionada con la seguridad, como acceder directamente a un área protegida, se genera una excepción de falla segura.

Un ejemplo de Hello World seguro

El SDK para LPCXpresso55S69 viene con algunos ejemplos de TrustZone que se pueden cargar en MCUXpresso. Como se mencionó anteriormente, estos ejemplos constan de dos proyectos separados:la parte segura y el código de usuario no seguro.

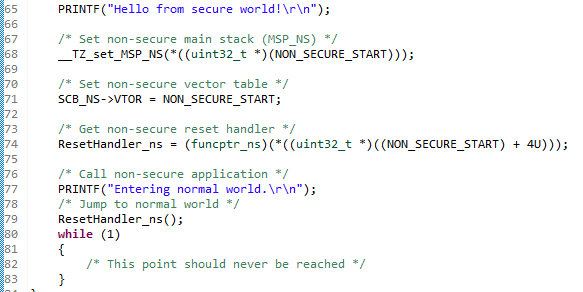

La parte segura se ve casi exactamente como cualquier otro proyecto de MCUXpresso. Sin embargo, hay una diferencia, que es la siguiente llamada a la función:

Esta función debería llamarse lo antes posible. Después de eso, es responsabilidad del proyecto seguro configurar la memoria y el proyecto no seguro:

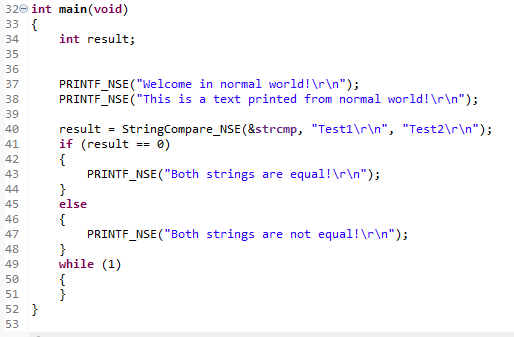

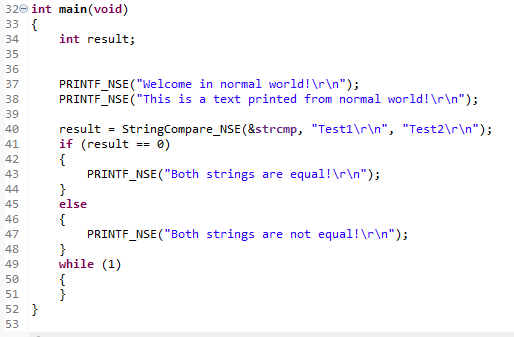

Debido a que el proyecto seguro maneja todas las llamadas de configuración, el proyecto no seguro no tiene que hacerlo, por lo que su función principal es corta:

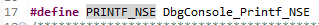

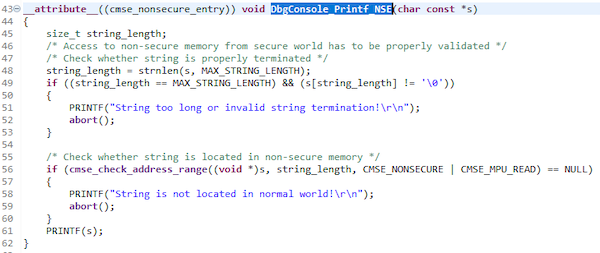

Sin embargo, esta aplicación solo llama a funciones seguras que se definieron en el otro proyecto. La siguiente definición para la función PRINTF_NSE es como se muestra:

Si se sigue esa definición, apunta a la tabla de chapa, definida en el proyecto asegurado. Es importante recordar que el proyecto no seguro solo conoce el archivo de encabezado que describe la tabla de revestimiento. Sin embargo, en este caso, podemos echar un vistazo a la función correspondiente en el código fuente:

La decoración "__attribute __ ((cmse_nonsecure_entry))" obliga a exportar la función al archivo de objeto.

Partición de la memoria

Los atributos de seguridad definen qué partes de la memoria están protegidas, NSC o no protegidas. Estos se comprueban con cada acceso. Para ello, la MCU se amplió con hardware que maneja estas comprobaciones y consta de tres bloques lógicos:

- Unidad de atribución de seguridad (SAU)

- Unidad de atribución definida por la implementación (IDAU)

- Lógica de atribución de seguridad

La SAU es programada por el proyecto seguro dentro de la función BOARD_InitTrustZone (). Esto permite que la memoria se particione en ocho regiones con diferentes configuraciones de seguridad. Tenga en cuenta que cualquier región que no se establezca explícitamente permanece segura de forma predeterminada.

El IDAU permite al fabricante de MCU, NXP en este caso, definir más regiones personalizadas. Aquí, las regiones dependen del bit 28 de la dirección. En la MCU LPC55S69, la parte inferior del mapa de memoria (0x0000_0000 a 0x2FFF_FFFF) tiene como valor predeterminado no seguro, por lo que es libre de configurar con la SAU.

El árbitro se asegura de que las configuraciones IDAU y SAU coincidan. Para que una región de memoria se marque como no segura, ambos bloques lógicos deben configurarse como no seguros. De lo contrario, la memoria volverá al estado seguro predeterminado. Lo mismo se aplica a las regiones de memoria NSC. Para que una sección sea NSC, la SAU debe estar marcada como NSC y la IDAU debe configurarse como no segura.

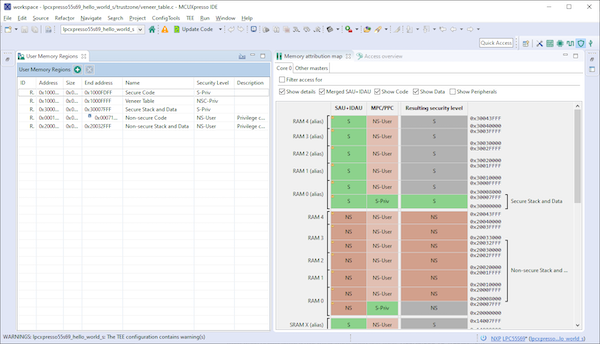

Hay una herramienta dentro de MCUXpresso que permite al usuario definir regiones de memoria rápida y fácilmente. Para acceder a la herramienta, use la barra de menú principal del IDE y abra la perspectiva TEE:

Figura 5. Esta herramienta MCUXpresso permite al usuario ver y editar el mapa de memoria de la MCU.

La tabla del lado izquierdo de la herramienta puede cambiar el nivel de seguridad de las regiones de memoria. El mapa de memoria en el lado derecho ilustra cómo se particiona la memoria.

TrustZone ofrece un componente de seguridad necesario

En la serie LPC5500 MCU con tecnología TrustZone, la memoria se divide en un mundo seguro y otro no seguro; es posible permitir que los usuarios accedan a partes de la memoria no segura, y también se puede escribir una aplicación segura para ser utilizada por otros. TrustZone actúa como un guardián entre los dos mundos y gestiona cómo el núcleo pasa entre ellos.

Se introdujeron dos nuevas instrucciones a tal efecto. La aplicación segura proporciona una tabla de revestimiento que expone las funciones que se pueden llamar desde el contexto no seguro. El hardware de la MCU garantiza que no se realicen operaciones ilegales de acceso a la memoria. Este hardware también se puede utilizar para configurar las regiones en el mapa de memoria. Para ese propósito, MCUXpresso ofrece la perspectiva TEE. Una comprensión más profunda de la seguridad proporcionada por la serie LPC5500 de MCU permite una mejor experiencia de diseño. Puede encontrar más información sobre TrustZone en TrustZone:Calling the Secure World.

Los artículos de la industria son una forma de contenido que permite a los socios de la industria compartir noticias, mensajes y tecnología útiles con los lectores de All About Circuits de una manera que el contenido editorial no es adecuado. Todos los artículos de la industria están sujetos a estrictas pautas editoriales con la intención de ofrecer a los lectores noticias útiles, experiencia técnica o historias. Los puntos de vista y las opiniones expresados en los artículos de la industria son los del socio y no necesariamente los de All About Circuits o sus redactores.

Computación en la nube

- La nube y cómo está cambiando el mundo de las TI

- Cloud Security es el futuro de la ciberseguridad

- Cómo convertirse en ingeniero de seguridad en la nube

- Por qué el futuro de la seguridad de los datos en la nube es programable

- ¿Cómo proteger la tecnología en la nube?

- Cómo administrar los riesgos de seguridad en la nube

- Cómo los piratas informáticos piratean la nube; Agregue más seguridad a su nube con AWS

- ¿Cómo aprobar el examen de ingeniero de Google Cloud?

- Cómo implementar DevOps en la nube

- Cómo migrar ERP a la nube

- Cómo aprovechar los beneficios de la nube pública